# **Distributed synthesis** for synchronous systems<sup>1</sup>

Paul Gastin

LSV

ENS de Cachan & CNRS Paul.Gastin@lsv.ens-cachan.fr

Dec 6th, 2006

<sup>&</sup>lt;sup>1</sup>Joint work with Nathalie Sznajder and Marc Zeitoun

## Outline

Synthesis and control for sequential systems

## Synthesis and control for distributed systems

Well-connected architectures

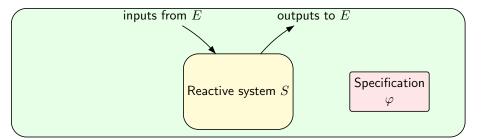

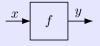

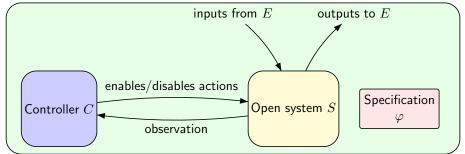

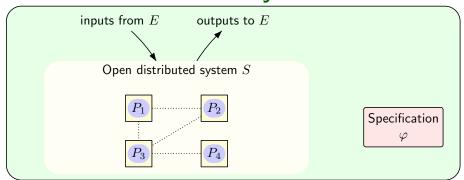

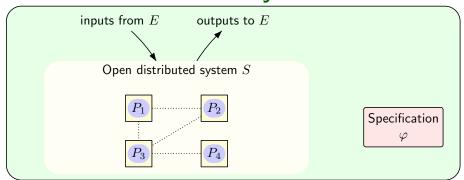

# **Open / Reactive system**

#### Synthesis problem

- Given a specification  $\varphi$ , decide whether there exists a program P such that  $P \| E \models \varphi$  for all environment E.

- Build such a program *P* (if one exists).

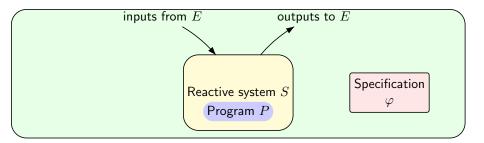

# **Open / Reactive system**

#### Synthesis problem

- Given a specification  $\varphi$ , decide whether there exists a program P such that  $P \| E \models \varphi$  for all environment E.

- Build such a program P (if one exists).

# Specification

#### Example: Elevator

- Inputs: call for level i.

- Outputs: open/close door i, move 1 level up/down.

#### Linear time: LTL, FO, MSO, regular, ...

- ▶ Safety:  $G(\texttt{level} \neq i \longrightarrow \texttt{is\_closed}_i)$

- Liveness:  $G(\texttt{is\_called}_i \longrightarrow F(\texttt{level} = i \land \texttt{is\_open}_i))$

#### Branching time: CTL, $CTL^*$ , $\mu$ -calculus, ...

- $AG(call_i) \top$  (call\_i is uncontrollable)

- AGEF(level =  $0 \land \texttt{is_open}_0$ )

# Specification

#### Example: Elevator

- Inputs: call for level i.

- Outputs: open/close door i, move 1 level up/down.

#### Linear time: LTL, FO, MSO, regular, ...

- Safety:  $G(\texttt{level} \neq i \longrightarrow \texttt{is\_closed}_i)$

- Liveness:  $G(\texttt{is\_called}_i \longrightarrow F(\texttt{level} = i \land \texttt{is\_open}_i))$

#### Branching time: CTL, CTL\*, $\mu$ -calculus, ...

- $AG(call_i) \top$  (call\_i is uncontrollable)

- AGEF(level =  $0 \land is\_open_0$ )

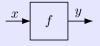

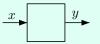

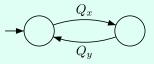

- $Q_x$ : domain for input variable x

- $Q_y$ : domain for output variable y

- Program:  $f: Q_x^+ \to Q_y$

- Input:  $x_1 x_2 \cdots \in Q_x^{\omega}$ .

- Behavior:  $(x_1, y_1)(x_2, y_2)(x_3, y_3) \cdots$  with  $y_n = f(x_1 \cdots x_n)$  for all n > 0.

### Chruch problem (implementability) 1962

- Given a linear time specification  $\varphi$  over the alphabet  $\Sigma = Q_x \times Q_y$ . Does there exist a program f such that all f-behaviors satisfy  $\varphi$ ?

- Given a branching time specification  $\varphi$  over the alphabet  $\Sigma = Q_x \times Q_y$ , Does there exist a program f such that its run-tree satisfies  $\varphi$ ?

- $Q_x$ : domain for input variable x

- $Q_y$ : domain for output variable y

- Program:  $f: Q_x^+ \to Q_y$

- Input:  $x_1 x_2 \cdots \in Q_x^{\omega}$ .

- Behavior:  $(x_1, y_1)(x_2, y_2)(x_3, y_3) \cdots$  with  $y_n = f(x_1 \cdots x_n)$  for all n > 0.

## Chruch problem (implementability) 1962

- Given a linear time specification φ over the alphabet Σ = Q<sub>x</sub> × Q<sub>y</sub>, Does there exist a program f such that all f-behaviors satisfy φ?

- Given a branching time specification  $\varphi$  over the alphabet  $\Sigma = Q_x \times Q_y$ , Does there exist a program f such that its run-tree satisfies  $\varphi$ ?

- $Q_x$ : domain for input variable x

- $Q_y$ : domain for output variable y

- Program:  $f: Q_x^+ \to Q_y$

- Input:  $x_1 x_2 \cdots \in Q_x^{\omega}$ .

- Behavior:  $(x_1, y_1)(x_2, y_2)(x_3, y_3) \cdots$  with  $y_n = f(x_1 \cdots x_n)$  for all n > 0.

## Chruch problem (implementability) 1962

- Given a linear time specification φ over the alphabet Σ = Q<sub>x</sub> × Q<sub>y</sub>, Does there exist a program f such that all f-behaviors satisfy φ?

- Given a branching time specification  $\varphi$  over the alphabet  $\Sigma = Q_x \times Q_y$ , Does there exist a program f such that its run-tree satisfies  $\varphi$ ?

## Chruch problem (implementability) 1962

Given a linear time specification  $\varphi$  over the alphabet  $\Sigma = Q_x \times Q_y$ , Does there exist a program f such that all f-behaviors satisfy  $\varphi$ ?

#### Implementability $\neq$ Satisfiability

•

$$Q_x = \{0, 1\}$$

and  $\varphi := \mathsf{F}(x = 1)$

- $\varphi$  is satisfiable:  $(1,0)^{\omega} \models \varphi$

- $\varphi$  is not implementable since the input is not controllable.

## Implementability $\neq$ Validity of $\forall \vec{x} \; \exists \vec{y} \; \varphi$

- $\blacktriangleright \ Q_x = Q_y = \{0,1\} \text{ and } \varphi := (y=1) \longleftrightarrow \mathsf{F}(x=1)$

- $\blacktriangleright \forall \vec{x} \exists \vec{y} \varphi \text{ is valid.}$

- $\varphi$  is not implementable by a reactive program.

For non-reactive terminating programs, Implementability = Validity of  $\forall \vec{x} \ \exists \vec{y} \ \varphi$

## Chruch problem (implementability) 1962

Given a linear time specification  $\varphi$  over the alphabet  $\Sigma = Q_x \times Q_y$ , Does there exist a program f such that all f-behaviors satisfy  $\varphi$ ?

#### Implementability $\neq$ Satisfiability

•

$$Q_x = \{0, 1\}$$

and  $\varphi := \mathsf{F}(x = 1)$

- $\varphi$  is satisfiable:  $(1,0)^{\omega} \models \varphi$

- $\varphi$  is not implementable since the input is not controllable.

## Implementability $\neq$ Validity of $\forall \vec{x} \exists \vec{y} \varphi$

- $\blacktriangleright \ Q_x = Q_y = \{0,1\} \text{ and } \varphi := (y=1) \longleftrightarrow \mathsf{F}(x=1)$

- $\blacktriangleright \ \forall \vec{x} \ \exists \vec{y} \ \varphi \text{ is valid.}$

- $\varphi$  is not implementable by a reactive program.

For non-reactive terminating programs, Implementability = Validity of  $\forall \vec{x} \ \exists \vec{y} \ \varphi$

## Chruch problem (implementability) 1962

Given a linear time specification  $\varphi$  over the alphabet  $\Sigma = Q_x \times Q_y$ , Does there exist a program f such that all f-behaviors satisfy  $\varphi$ ?

#### Implementability $\neq$ Satisfiability

•

$$Q_x = \{0, 1\}$$

and  $\varphi := \mathsf{F}(x = 1)$

- $\varphi$  is satisfiable:  $(1,0)^{\omega} \models \varphi$

- $\varphi$  is not implementable since the input is not controllable.

### Implementability $\neq$ Validity of $\forall \vec{x} \exists \vec{y} \varphi$

- $\blacktriangleright \ Q_x = Q_y = \{0,1\} \text{ and } \varphi := (y=1) \longleftrightarrow \mathsf{F}(x=1)$

- $\blacktriangleright \forall \vec{x} \exists \vec{y} \varphi \text{ is valid.}$

- $\blacktriangleright \varphi$  is not implementable by a reactive program.

For non-reactive terminating programs, Implementability = Validity of  $\forall \vec{x} \ \exists \vec{y} \ \varphi$

## Chruch problem (implementability) 1962

Given a linear time specification  $\varphi$  over the alphabet  $\Sigma = Q_x \times Q_y$ , Does there exist a program f such that all f-behaviors satisfy  $\varphi$ ?

#### Theorem (Pnueli-Rosner 89)

- The specification  $\varphi \in \mathrm{LTL}$  is implementable iff the formula

$$\mathsf{A}\,\varphi\wedge\mathsf{AG}(\bigwedge_{a\in Q_x}\mathsf{EX}(x=a))$$

is satisfiable.

When φ is implementable, we can construct a finite state implementation (program) in time doubly exponential in φ.

## **Control problem**

## Open system: Transitions system $\mathcal{A} = (Q, \Sigma, q_0, \delta)$

- Q: finite or infinite set of states,

- $\delta$ : deterministic or non deterministic transition function.

#### Control problem

- Given a system S and a specification  $\varphi$ , decide whether there exists a controller C such that  $(S \otimes C) ||E| \models \varphi$ .

- Build such a controller C (if one exists).

# **Control problem**

## Open system: Transitions system $\mathcal{A} = (Q, \Sigma, q_0, \delta)$

- Q: finite or infinite set of states,

- $\delta$ : deterministic or non deterministic transition function.

## Control problem

- ► Given a system S and a specification  $\varphi$ , decide whether there exists a controller C such that  $(S \otimes C) ||E| \models \varphi$ .

- Build such a controller C (if one exists).

# **Control versus Game**

| Correspondance        |                                               |

|-----------------------|-----------------------------------------------|

| Transition system     | = Game arena (graph).                         |

| Controllable events   | = Actions of player 1 (controller).           |

| Uncontrollable events | = Action of player 0 (opponent, environment). |

| Behavior              | = Play.                                       |

| Controller            | = Strategy.                                   |

| Specification         | <ul> <li>Winning condition.</li> </ul>        |

| Finding a controller  | = finding a winning strategy.                 |

#### Theorem: Büchi - Landweber 1969

If the system is finite state and the specification is regular then the control problem is decidable.

Moreover, when  $(S, \varphi)$  is controllable, we can synthesize a finite state controller.

# **Control versus Game**

| Correspondance        |                                               |

|-----------------------|-----------------------------------------------|

| Transition system     | = Game arena (graph).                         |

| Controllable events   | = Actions of player 1 (controller).           |

| Uncontrollable events | = Action of player 0 (opponent, environment). |

| Behavior              | = Play.                                       |

| Controller            | = Strategy.                                   |

| Specification         | <ul> <li>Winning condition.</li> </ul>        |

| Finding a controller  | = finding a winning strategy.                 |

#### Theorem: Büchi - Landweber 1969

If the system is finite state and the specification is regular then the control problem is decidable.

Moreover, when  $(S, \varphi)$  is controllable, we can synthesize a finite state controller.

# Program synthesis versus System control

#### Equivalence

The implementability problem for

is equivalent to the control problem for the system

## Outline

## Synthesis and control for sequential systems

2 Synthesis and control for distributed systems

Well-connected architectures

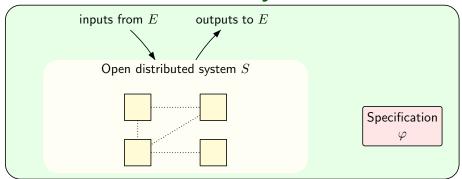

## **Distributed** synthesis

Distributed synthesis problem

- Decide whether there exists a distributed program st.  $P_1 \parallel \cdots \parallel P_n \parallel E \models \varphi.$

- Synthesis: If so, compute such a distributed program.

#### Peterson-Reif 1979, Pnueli-Rosner 1990

In general, the problem is undecidable.

## **Distributed** synthesis

#### Distributed synthesis problem

Decide whether there exists a distributed program st.  $P_1 \parallel \cdots \parallel P_n \parallel E \models \varphi.$

Synthesis: If so, compute such a distributed program.

#### Peterson-Reif 1979, Pnueli-Rosner 1990

In general, the problem is undecidable.

## **Distributed** synthesis

#### Distributed synthesis problem

Decide whether there exists a distributed program st.  $P_1 \parallel \cdots \parallel P_n \parallel E \models \varphi.$

Synthesis: If so, compute such a distributed program.

#### Peterson-Reif 1979, Pnueli-Rosner 1990

In general, the problem is undecidable.

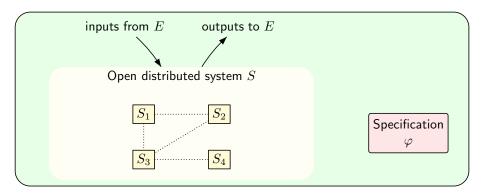

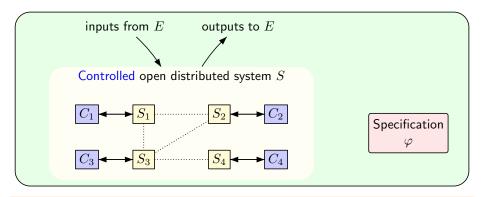

## **Distributed** control

#### Distributed control problem

- Decide whether there exists a distributed controller st.  $(S_1 \otimes C_1) \parallel \cdots \parallel (S_n \otimes C_n) \parallel E \models \varphi.$

- Synthesis: If so, compute such a distributed controller.

## **Distributed** control

#### Distributed control problem

Decide whether there exists a distributed controller st.  $(S_1 \otimes C_1) \parallel \cdots \parallel (S_n \otimes C_n) \parallel E \models \varphi.$

Synthesis: If so, compute such a distributed controller.

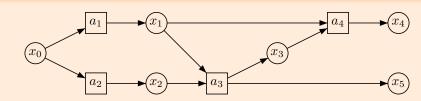

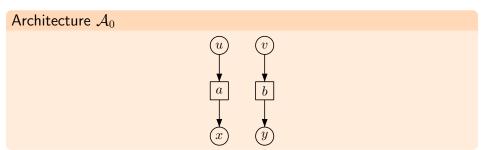

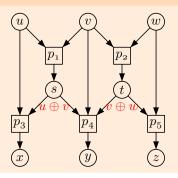

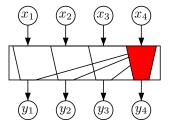

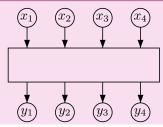

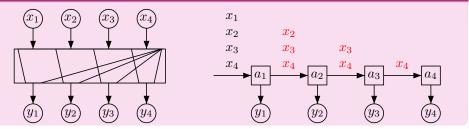

## Architectures with shared variables

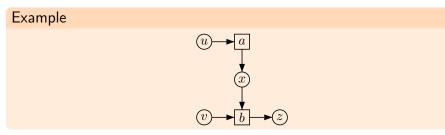

## Example

## Architecture $\mathcal{A} = (\mathcal{P}, \mathcal{V}, R, W)$

- ▶ *P* finite set of processes/agents.

- V finite set of Variables.

- $\blacktriangleright \ R \subseteq \mathcal{P} \times \mathcal{V}: \quad (a, x) \in R \text{ iff } a \text{ reads } x.$

- R(a) variables read by process  $a \in \mathcal{P}_{a}$

- $R^{-1}(x)$  processes reading variable  $x \in \mathcal{V}$ .

- $W \subseteq \mathcal{P} \times \mathcal{V}$ :  $(a, x) \in W$  iff a writes to x.

- W(a) variables written by process  $a \in \mathcal{P}$ ,

- $W^{-1}(x)$  processes writing to variable  $x \in \mathcal{V}$ .

## Architectures with shared variables

## Example

## Architecture $\mathcal{A} = (\mathcal{P}, \mathcal{V}, R, W)$

- $\mathcal{P}$  finite set of processes/agents.

- V finite set of Variables.

- $R \subseteq \mathcal{P} \times \mathcal{V}$ :  $(a, x) \in R$  iff a reads x.

- R(a) variables read by process  $a \in \mathcal{P}$ ,

- $R^{-1}(x)$  processes reading variable  $x \in \mathcal{V}$ .

- $W \subseteq \mathcal{P} \times \mathcal{V}$ :  $(a, x) \in W$  iff a writes to x.

- W(a) variables written by process  $a \in \mathcal{P}$ ,

- $W^{-1}(x)$  processes writing to variable  $x \in \mathcal{V}$ .

#### Main parameters

- Which subclass of architectures?

- Which semantics?

synchronous (with our without delay), asynchronous

What kind of specification?

LTL, CLT\*, µ-calculus Rational, Recognizable word/tree

#### Main parameters

- Which subclass of architectures?

- Which semantics?

#### synchronous (with our without delay), asynchronous

What kind of specification?

LTL, CLT\*, µ-calculus Rational, Recognizable word/tree

#### Main parameters

- Which subclass of architectures?

- Which semantics?

synchronous (with our without delay), asynchronous

What kind of specification?

LTL, CLT\*,  $\mu$ -calculus Rational, Recognizable word/tree

#### Main parameters

- Which subclass of architectures?

- Which semantics?

synchronous (with our without delay), asynchronous

What kind of specification?

LTL, CLT\*,  $\mu$ -calculus Rational, Recognizable word/tree

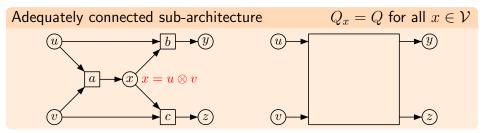

## **0-delay synchronous semantics**

#### Example

Programs with local memory:  $f_x : Q_u^* \to Q_x$  and  $f_z : (Q_x \times Q_v)^* \to Q_z$ .

Input:

$$\begin{pmatrix}

u_1 & u_2 & u_3 & \cdots \\

v_1 & v_2 & v_3 & \cdots

\end{pmatrix} \in (Q_u \times Q_v)^{\omega}.$$

Behavior:

$$\begin{pmatrix}

u_1 & u_2 & u_3 & \cdots \\

v_1 & v_2 & v_3 & \cdots \\

x_1 & x_2 & x_3 & \cdots \\

z_1 & z_2 & z_3 & \cdots

\end{pmatrix}$$

with

$$\begin{cases}

x_n = f_x(u_1 \cdots u_n) \\

z_n = f_z((x_1, v_1) \cdots (x_n, v_n))

\end{cases}$$

for all  $n > 0$ .

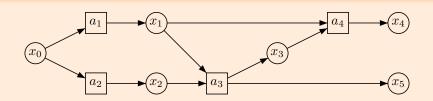

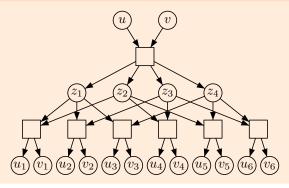

## **Global versus distributed synthesis**

## Network information flow

#### Lemma (Rasala Lehman–Lehman 2004)

If  $f^1, \ldots, f^n : S^2 \to S$  are pairwise independent functions, then  $n \leq |S| + 1$ .  $f^i, f^j$  are independent if  $(f^i, f^j) : S^2 \to S^2$  is one to one.

## Global versus distributed synthesis

# Network information flow $(u_1)(v_1)(u_2)(v_2)(u_3)(v_3)(u_4)(v_4)(u_5)(v_5)(u_6)(v_6)$

#### Lemma (Rasala Lehman–Lehman 2004)

If  $f^1, \ldots, f^n : S^2 \to S$  are pairwise independent functions, then  $n \leq |S| + 1$ .  $f^i, f^j$  are independent if  $(f^i, f^j) : S^2 \to S^2$  is one to one.

## **Global versus distributed synthesis**

#### Network information flow

## Lemma (Rasala Lehman–Lehman 2004)

If  $f^1, \ldots, f^n : S^2 \to S$  are pairwise independent functions, then  $n \leq |S| + 1$ .  $f^i, f^j$  are independent if  $(f^i, f^j) : S^2 \to S^2$  is one to one.

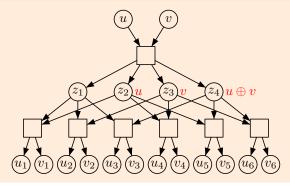

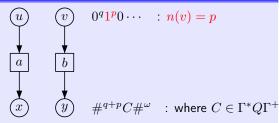

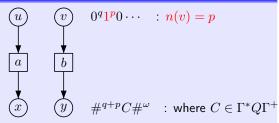

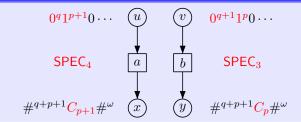

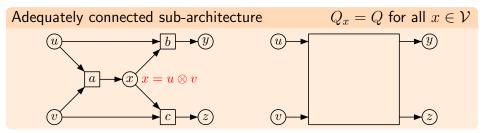

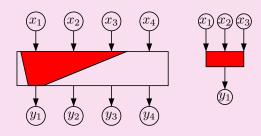

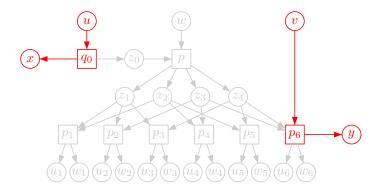

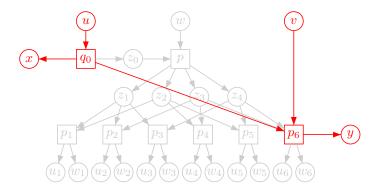

# Undecidability

## Theorem (Pnueli-Rosner FOCS'90)

The synthesis problem for architecture  $A_0$  and LTL (or CTL) specifications is undecidable.

#### Proof

Reduction from the halting problem on the empty tape.

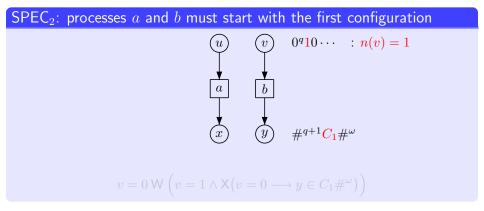

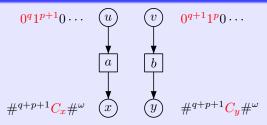

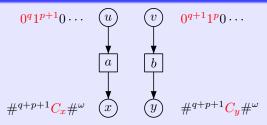

# Undecidability proof 1

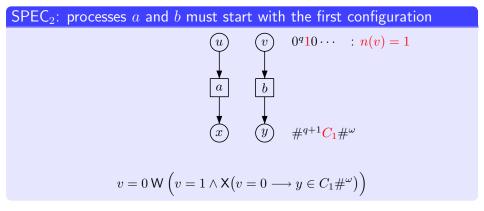

SPEC<sub>1</sub>: processes a and b must output configurations

$$(v = 0 \land y = \#) \ \mathsf{W} \left( v = 1 \land (v = 1 \land y = \#) \ \mathsf{W} \left( v = 0 \land y \in \Gamma^* Q \Gamma^+ \#^\omega \right) \right)$$

where

$y \in \Gamma^* Q \Gamma^+ \#^\omega \quad \stackrel{\mathsf{def}}{=} \quad y \in \Gamma \, \mathsf{U} \left( y \in Q \land \mathsf{X} \big( y \in \Gamma \, \mathsf{U} \, (y \in \Gamma \land \mathsf{X} \, \mathsf{G} \, y = \#) \big) \right)$

SPEC<sub>1</sub>: processes a and b must output configurations

$$(v = 0 \land y = \#) \mathsf{W} \left( v = 1 \land (v = 1 \land y = \#) \mathsf{W} \left( v = 0 \land y \in \Gamma^* Q \Gamma^+ \#^\omega \right) \right)$$

where

$$y \in \Gamma^* Q \Gamma^+ \#^\omega \quad \stackrel{\text{def}}{=} \quad y \in \Gamma \, \mathsf{U} \left( y \in Q \land \mathsf{X} \big( y \in \Gamma \, \mathsf{U} \, (y \in \Gamma \land \mathsf{X} \, \mathsf{G} \, y = \#) \big) \right)$$

$n(u) = n(v) \longrightarrow \mathsf{G}(x = y)$

where

$n(u) = n(v) \stackrel{\text{def}}{=} (u = v = 0) \cup (u = v = 1 \land (u = v = 1 \cup u = v = 0))$

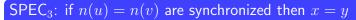

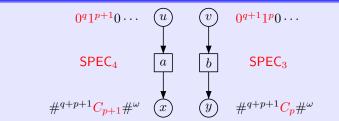

SPEC<sub>3</sub>: if n(u) = n(v) are synchronized then x = y

$$n(u) = n(v) \longrightarrow \mathsf{G}(x = y)$$

where

$$n(u) = n(v) \quad \stackrel{\mathrm{def}}{=} \quad (u = v = 0) \ \mathrm{U} \ (u = v = 1 \land (u = v = 1 \ \mathrm{U} \ u = v = 0))$$

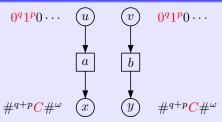

SPEC<sub>4</sub>: if n(u) = n(v) + 1 are synchronized then  $C_y \vdash C_x$

$$n(u) = n(v) + 1 \longrightarrow x = y \cup (\operatorname{Trans}(y, x) \wedge X^3 \operatorname{G} x = y)$$

where Trans(y, x) is defined by

$\bigvee_{p,a,q,b,\leftarrow)\in T,c\in\Gamma} (y=cpa\wedge x=qcb) \quad \lor \bigvee_{(p,a,q,b,\rightarrow)\in T,c\in\Gamma} (y=pac\wedge x=bqc)$

$$\vee \bigvee_{(p,a,q,b,\to)\in T} (y = pa \# \land x = bq \Box)$$

SPEC<sub>4</sub>: if n(u) = n(v) + 1 are synchronized then  $C_y \vdash C_x$

$$n(u) = n(v) + 1 \longrightarrow x = y \cup \left(\operatorname{Trans}(y, x) \wedge \mathsf{X}^3 \operatorname{\mathsf{G}} x = y\right)$$

where Trans(y, x) is defined by

$\bigvee_{\substack{(p,a,q,b,\leftarrow)\in T,c\in\Gamma}} (y = cpa \land x = qcb) \qquad \lor \qquad \bigvee_{\substack{(p,a,q,b,\rightarrow)\in T,c\in\Gamma}} (y = pac \land x = bqc) \\ \lor \qquad \bigvee_{\substack{(p,a,q,b,\rightarrow)\in T}} (y = pa\# \land x = bq\Box)$

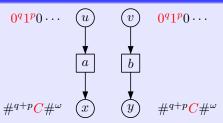

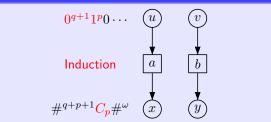

#### Lemma: winning strategies must simulate the Turing machine

For each  $p \ge 1$ , if n(u) = p then  $C_x = C_p$  is the *p*-th configuration of the Turing machine starting from the empty tape.

# Proof $\begin{array}{cccc} & u & v \\ & u & v \\ & a & b \\ & & b \\ & & & y \\ & & & y \\ \end{array}$

#### Corollary

#### Lemma: winning strategies must simulate the Turing machine

For each  $p \ge 1$ , if n(u) = p then  $C_x = C_p$  is the *p*-th configuration of the Turing machine starting from the empty tape.

##

#### Corollary

#### Lemma: winning strategies must simulate the Turing machine

For each  $p \ge 1$ , if n(u) = p then  $C_x = C_p$  is the *p*-th configuration of the Turing machine starting from the empty tape.

#### Proof

#### Corollary

#### Lemma: winning strategies must simulate the Turing machine

For each  $p \ge 1$ , if n(u) = p then  $C_x = C_p$  is the *p*-th configuration of the Turing machine starting from the empty tape.

####

#### Corollary

#### Lemma: winning strategies must simulate the Turing machine

For each  $p \ge 1$ , if n(u) = p then  $C_x = C_p$  is the *p*-th configuration of the Turing machine starting from the empty tape.

#### Proof

#### Corollary

#### Lemma: winning strategies must simulate the Turing machine

For each  $p \ge 1$ , if n(u) = p then  $C_x = C_p$  is the *p*-th configuration of the Turing machine starting from the empty tape.

#### Proof

#### Corollary

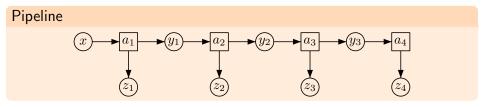

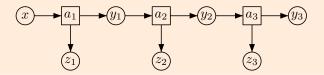

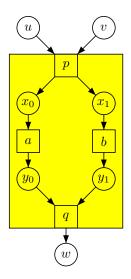

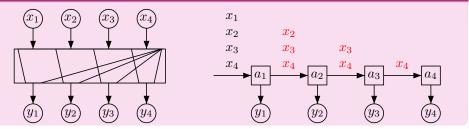

### Decidability of distributed synthesis

#### Pnueli-Rosner (FOCS'90)

The synthesis problem for pipeline architectures and LTL specifications is non elementary decidable.

#### Peterson-Reif (FOCS'79)

multi-person games with incomplete information.

$\implies$  non-elementary lower bound for the synthesis problem.

#### Kupferman-Vardi (LICS'01)

The synthesis problem is non elementary decidable for

- one-way chain, one-way ring, two-way chain and two-way ring,

- CTL\* specifications (or tree-automata specifications) on all variables,

- synchronous, 1-delay semantics,

- local strategies.

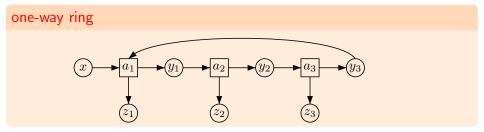

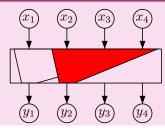

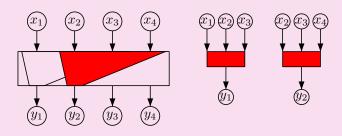

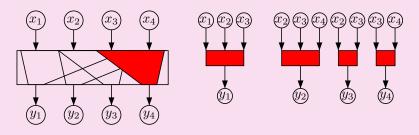

#### one-way chain

#### Kupferman-Vardi (LICS'01)

The synthesis problem is non elementary decidable for

- one-way chain, one-way ring, two-way chain and two-way ring,

- CTL\* specifications (or tree-automata specifications) on all variables,

- synchronous, 1-delay semantics,

- local strategies.

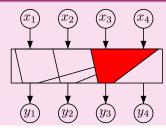

#### Kupferman-Vardi (LICS'01)

The synthesis problem is non elementary decidable for

- one-way chain, one-way ring, two-way chain and two-way ring,

- CTL\* specifications (or tree-automata specifications) on all variables,

- synchronous, 1-delay semantics,

- local strategies.

#### two-way chain

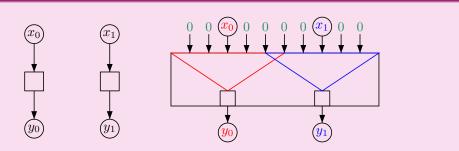

### 1-delay synchronous semantics

Programs:  $f_x : Q_u^* \to Q_x$  and  $f_z : (Q_x \times Q_v)^* \to Q_z$ . • Input:  $\begin{pmatrix} u_1 & u_2 & u_3 & \cdots \\ v_1 & v_2 & v_3 & \cdots \end{pmatrix} \in (Q_u \times Q_v)^{\omega}$ . • Behavior:  $\begin{pmatrix} u_1 & u_2 & u_3 & \cdots \\ v_1 & v_2 & v_3 & \cdots \\ x_1 & x_2 & x_3 & \cdots \\ z_1 & z_2 & z_3 & \cdots \end{pmatrix}$ with  $\begin{cases} x_{n+1} = f_x(u_1 \cdots u_n) \\ z_{n+1} = f_z((x_1, v_1) \cdots (x_n, v_n)) \end{cases}$  for all n > 0.

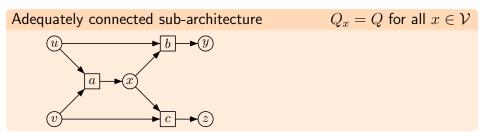

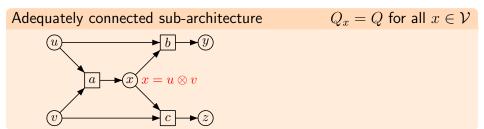

- An adequately connected architecture is equivalent to a singleton architecture.

- The synthesis problem is decidable for LTL specifications and pipelines of adequately connected architectures.

- > An adequately connected architecture is equivalent to a singleton architecture.

- The synthesis problem is decidable for LTL specifications and pipelines of adequately connected architectures.

- > An adequately connected architecture is equivalent to a singleton architecture.

- The synthesis problem is decidable for LTL specifications and pipelines of adequately connected architectures.

- > An adequately connected architecture is equivalent to a singleton architecture.

- The synthesis problem is decidable for LTL specifications and pipelines of adequately connected architectures.

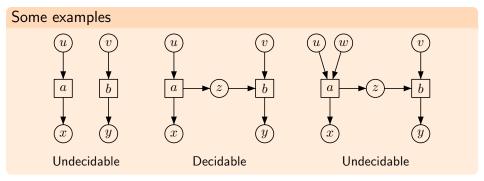

### Information fork criterion (Finkbeiner–Schewe LICS '05)

### Information fork criterion (Finkbeiner–Schewe LICS '05)

### Information fork criterion (Finkbeiner–Schewe LICS '05)

### Outline

#### Synthesis and control for sequential systems

Synthesis and control for distributed systems

Well-connected architectures

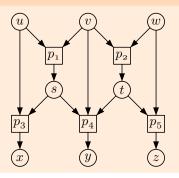

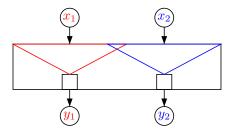

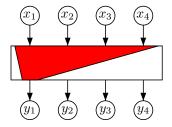

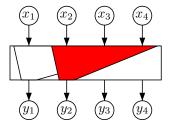

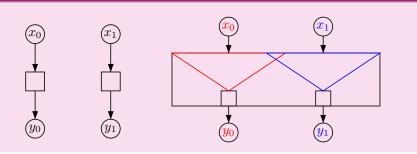

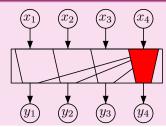

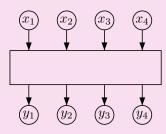

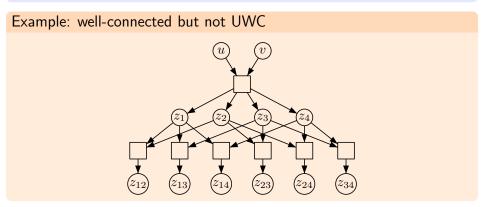

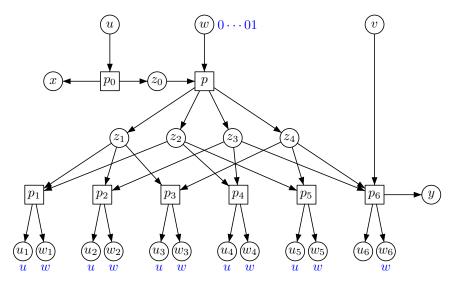

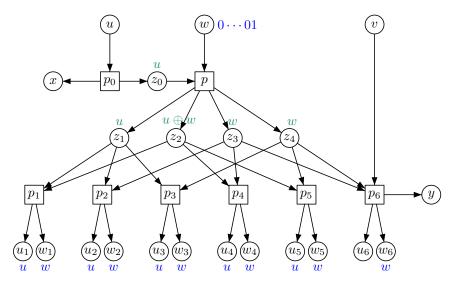

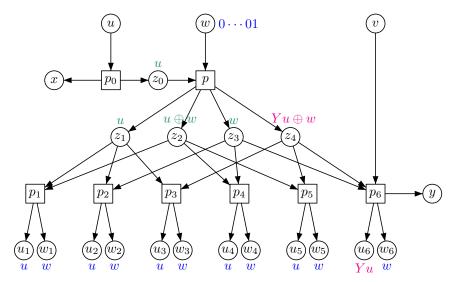

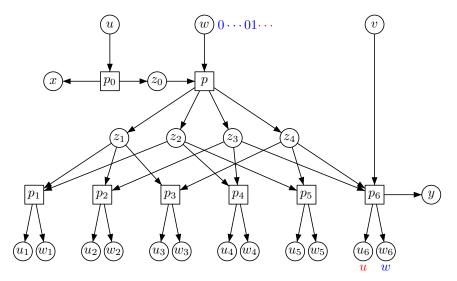

#### Definition

For an output variable y, View(y) is the set of input variables x such that there is a path from x to y.

#### Definition

An architecture is uniformly well connected if there is a uniform way to route variables in View(y) to y for each output variable y.

#### Example

#### Definition

For an output variable y, View(y) is the set of input variables x such that there is a path from x to y.

#### Definition

An architecture is uniformly well connected if there is a uniform way to route variables in View(y) to y for each output variable y.

#### Example

#### Definition

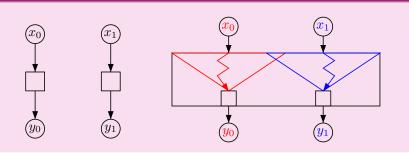

An architecture is uniformly well connected if there is a uniform way to route variables in View(v) to v for each output variable v.

- If the capacity of internal variables is big enough then the architecture is uniformly well-connected.

- If the architecture is uniformly well-connected then we can use causal strategies instead of local ones.

#### Proposition

Checking whether a given architecture is uniformly well connected is NP-complete.

#### Proof

Reduction to the multicast problem in Network Information Flow. The multicast problem is NP-complete (Rasala Lehman-Lehman 2004).

#### Definition

An architecture is uniformly well connected if there is a uniform way to route variables in View(v) to v for each output variable v.

- If the capacity of internal variables is big enough then the architecture is uniformly well-connected.

- If the architecture is uniformly well-connected then we can use causal strategies instead of local ones.

#### Proposition

Checking whether a given architecture is uniformly well connected is NP-complete.

#### Proof

Reduction to the multicast problem in Network Information Flow. The multicast problem is NP-complete (Rasala Lehman-Lehman 2004).

#### Definition

An architecture has uncomparable information if there exist  $y_1, y_2$  output variables such that  $View(y_2) \setminus View(y_1) \neq \emptyset$  and  $View(y_1) \setminus View(y_2) \neq \emptyset$ .

#### Definition

An architecture has uncomparable information if there exist  $y_1, y_2$  output variables such that  $View(y_2) \setminus View(y_1) \neq \emptyset$  and  $View(y_1) \setminus View(y_2) \neq \emptyset$ .

#### Definition

An architecture has uncomparable information if there exist  $y_1, y_2$  output variables such that  $View(y_2) \setminus View(y_1) \neq \emptyset$  and  $View(y_1) \setminus View(y_2) \neq \emptyset$ .

#### Definition

An architecture has uncomparable information if there exist  $y_1, y_2$  output variables such that  $View(y_2) \setminus View(y_1) \neq \emptyset$  and  $View(y_1) \setminus View(y_2) \neq \emptyset$ .

#### Definition

An architecture has uncomparable information if there exist  $y_1, y_2$  output variables such that  $View(y_2) \setminus View(y_1) \neq \emptyset$  and  $View(y_1) \setminus View(y_2) \neq \emptyset$ .

# Uncomparable information yields undecidability

#### Theorem

Architectures with uncomparable information are undecidable for LTL or CTL inputoutput specifications.

# Uncomparable information yields undecidability

#### Theorem

Architectures with uncomparable information are undecidable for LTL or CTL inputoutput specifications.

# Uncomparable information yields undecidability

#### Theorem

Architectures with uncomparable information are undecidable for LTL or CTL inputoutput specifications.

### Theorem (PG, Nathalie Sznajder, Marc Zeitoun)

Uniformly well connected architectures with preordered information are decidable for CTL\* external specifications.

#### Proof.

### Theorem: Kupferman-Vardi (LICS'01)

### Theorem (PG, Nathalie Sznajder, Marc Zeitoun)

Uniformly well connected architectures with preordered information are decidable for CTL\* external specifications.

#### Proof.

### Theorem: Kupferman-Vardi (LICS'01)

### Theorem (PG, Nathalie Sznajder, Marc Zeitoun)

Uniformly well connected architectures with preordered information are decidable for CTL\* external specifications.

#### Proof.

### Theorem: Kupferman-Vardi (LICS'01)

### Theorem (PG, Nathalie Sznajder, Marc Zeitoun)

Uniformly well connected architectures with preordered information are decidable for CTL\* external specifications.

### Proof.

### Theorem: Kupferman-Vardi (LICS'01)

### Theorem (PG, Nathalie Sznajder, Marc Zeitoun)

Uniformly well connected architectures with preordered information are decidable for CTL\* external specifications.

### Proof.

### Theorem: Kupferman-Vardi (LICS'01)

### Theorem (PG, Nathalie Sznajder, Marc Zeitoun)

Uniformly well connected architectures with preordered information are decidable for CTL\* external specifications.

### Proof.

### Theorem: Kupferman-Vardi (LICS'01)

### Theorem (PG, Nathalie Sznajder, Marc Zeitoun)

Uniformly well connected architectures with preordered information are decidable for CTL\* external specifications.

### Proof.

### Theorem: Kupferman-Vardi (LICS'01)

### Definition

A specification  $\varphi$  is robust if it can be written  $\varphi = \bigvee \bigwedge_{z \in \text{Out}} \varphi_z$  where  $\varphi_z$  depends only on  $\text{View}(z) \cup \{z\}$ .

#### Theorem

The synthesis problem for uniformly well-connected architectures and external and robust CTL\* specifications is decidable.

### Definition

A specification  $\varphi$  is robust if it can be written  $\varphi = \bigvee \bigwedge_{z \in \text{Out}} \varphi_z$  where  $\varphi_z$  depends only on  $\text{View}(z) \cup \{z\}$ .

#### Theorem

The synthesis problem for uniformly well-connected architectures and external and robust CTL\* specifications is decidable.

### Definition

A specification  $\varphi$  is robust if it can be written  $\varphi = \bigvee \bigwedge_{z \in \text{Out}} \varphi_z$  where  $\varphi_z$  depends only on  $\text{View}(z) \cup \{z\}$ .

#### Theorem

The synthesis problem for uniformly well-connected architectures and external and robust CTL\* specifications is decidable.

### Definition

A specification  $\varphi$  is robust if it can be written  $\varphi = \bigvee \bigwedge_{z \in \text{Out}} \varphi_z$  where  $\varphi_z$  depends only on  $\text{View}(z) \cup \{z\}$ .

#### Theorem

The synthesis problem for uniformly well-connected architectures and external and robust CTL\* specifications is decidable.

### Definition

A specification  $\varphi$  is robust if it can be written  $\varphi = \bigvee \bigwedge_{z \in \text{Out}} \varphi_z$  where  $\varphi_z$  depends only on  $\text{View}(z) \cup \{z\}$ .

#### Theorem

The synthesis problem for uniformly well-connected architectures and external and robust CTL\* specifications is decidable.

### Definition

A specification  $\varphi$  is robust if it can be written  $\varphi = \bigvee \bigwedge_{z \in \text{Out}} \varphi_z$  where  $\varphi_z$  depends only on  $\text{View}(z) \cup \{z\}$ .

#### Theorem

The synthesis problem for uniformly well-connected architectures and external and robust CTL\* specifications is decidable.

### Definition

A specification  $\varphi$  is robust if it can be written  $\varphi = \bigvee \bigwedge_{z \in Out} \varphi_z$  where  $\varphi_z$  depends only on  $View(z) \cup \{z\}$ .

#### Theorem

The synthesis problem for uniformly well-connected architectures and external and robust CTL\* specifications is decidable.

### Well-connected architectures

### Definition

An architecture is well connected if, for each output variable y, the subarchitecture formed by  $(E^*)^{-1}(y)$  is uniformly well connected.

### Well-connected architectures

#### Definition

An architecture is well connected if, for each output variable y, the subarchitecture formed by  $(E^*)^{-1}(y)$  is uniformly well connected.

#### Rasala Lehman–Lehman 2004

One can solve the network information flow in the special case where there is a unique sink in polynomial time.

#### Corollary

One can decide whether an architecture is well-connected in polynomial time.

### Well connected preordered architectures

#### Theorem

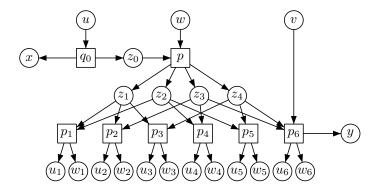

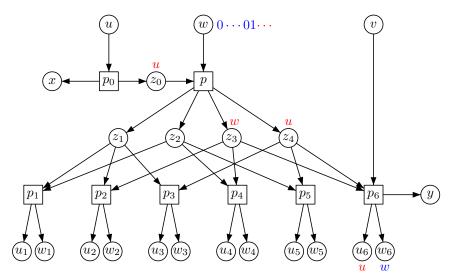

The synthesis problem for LTL specifications and well connected architectures with preordered information is undecidable.

### Well connected preordered architectures

#### Theorem

The synthesis problem for LTL specifications and well connected architectures with preordered information is undecidable.

### Well connected preordered architectures

#### Theorem

The synthesis problem for LTL specifications and well connected architectures with preordered information is undecidable.

One bit of u is hidden to  $p_6$

# **Open problem**

- Find a decidability criterium for external specifications and well-connected architectures.

- Find a decidability criterium for external specifications and arbitrary architectures.

- Decidability of the distributed control/synthesis problem for robust and external specifications.